# **Homework 3**

(Due date: March  $10^{\text{th}}$  @ 5:30 pm) Presentation and clarity are very important! Show your procedure!

## PROBLEM 1 (25 PTS)

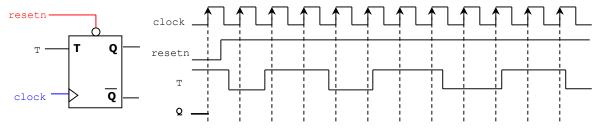

a) Complete the timing diagram of the circuit shown below. (5 pts)

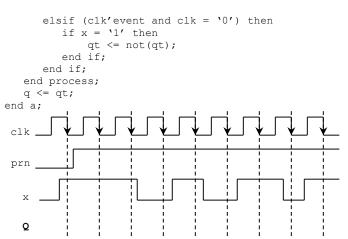

b) Complete the timing diagram of the circuit whose VHDL description is shown below: (5 pts)

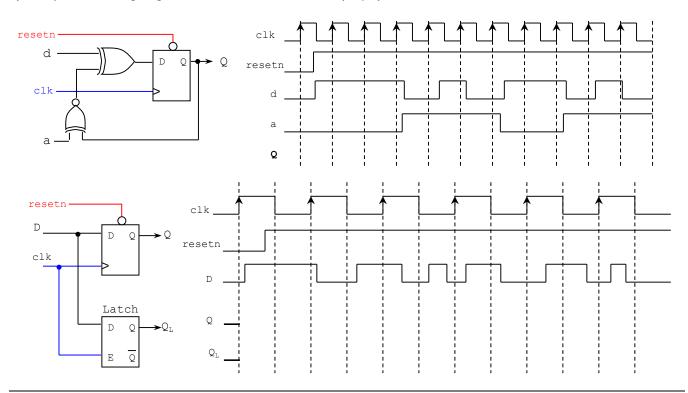

c) Complete the timing diagram of the circuits shown below: (15 pts)

# **PROBLEM 2 (15 PTS)**

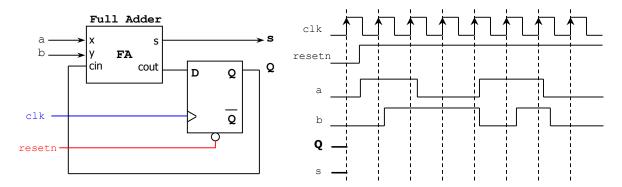

• Complete the timing diagram of the circuit shown below: (8 pts)

Complete the VHDL description of the synchronous sequential circuit whose truth table is shown below: (7 pts)

| prn | clk | A | В | Q <sub>t+1</sub> |

|-----|-----|---|---|------------------|

| 1   |     | 0 | 0 | Q <sub>t</sub>   |

| 1   |     | 0 | 1 | Q <sub>t</sub>   |

| 1   |     | 1 | 0 | В                |

| 1   |     | 1 | 1 | C                |

| 0   | X   | Χ | Х | 1                |

### **PROBLEM 3 (20 PTS)**

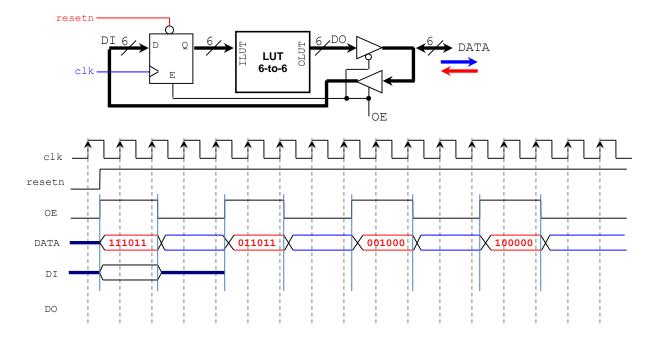

• Given the following circuit, complete the timing diagram (signals DO and DATA). The LUT 6-to-6 implements the following function:  $OLUT = [ILUT^{0.95}]$ . For example  $ILUT = 35 (100011_2) \rightarrow OLUT = [35^{0.95}] = 30 (011110_2)$

2

#### **PROBLEM 4 (30 PTS)**

- The following circuit is a 4-bit parallel/serial load shift register with enable input. Shifting operation: s 1=0. Parallel load: s 1=1. Note that  $Q = Q_3Q_2Q_1Q_0$ .  $D = D_3D_2D_1D_0$

- ✓ Write a structural VHDL code. You MUST create a file for: i) flip flop, ii) MUX 2-to-1, and iii) top file (where you will interconnect the flip flops and MUXes). Provide a printout. (10 pts)

- ✓ Write a VHDL testbench according to the timing diagram shown below. Complete the timing diagram by simulating your circuit (Timing Simulation). The clock frequency must be 50 MHz with 50% duty cycle. Provide a printout. (20 pts)

#### PROBLEM 5 (10 PTS)

Attach a printout of your Initial Project Report (no more than a page). This report should contain the project title, the project description, and the current status of the project. Use the provided template (Final Project - Report Template.docx).

3